Practica 7

1.- Diseñe un circuito combinacional cuyas entradas son dos números binarios enteros de 8 bits sin signo X y Y, y una señal de control MIN/MAX. La salida del circuito es un binario entero de 8 bits sin signo Z, tal que Z=0 si X=Y; de otra forma Z=Min(X,Y), si MIN/MAX=1 y Z=max(X,Y) si MIN/MAX=0.

Al aplicar un número mayor en la primera entrada (J1,J3) que en la entrada de menor peso (J2, J4) por lo tanto la salida se tendrá un cero lógico ya que en la compuerta 7408 se multiplica el uno lógico con el cero lógico y la multiplicación resultante es cero y después en la compuerta 7432N se suma este cero lógico o nivel bajo con otro nivel bajo y por lo tanto no encenderá el indicador (X7).

Figura 1. Circuito con salida a nivel bajo

Ahora si se aplica una señal mayor en la segunda entrada (J2, J4) que en la primera, se podrá encender el indicador (X7) ya que en el problema nos indica que si Min/Max=1 si F=max(X, Y).

Figura 2. Circuito con salida activa

La implementación se aprecia en la siguiente figura.

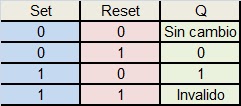

2.- Implemente el latch S-R con compuertas NAND y demostrar su tabla de verdad característica y su diagrama de tiempos.

Para comprobar la tabla de verdad se procede a implementar el circuito con ayuda del software de Multisim e ir variando las entradas S y R con el switch.

Cuando las entradas están en cero como se puede ver en la siguiente figura 3a, donde el switch J1 está abierto, quiere decir que el flip-flop está en estado de memoria pero si el switch es cerrado, figura 3b. Ocasionara que el flip-flop pase a un estado no permitido.

a) b)

Figura 3. flip-flop con compuertas NOR a) estado de memoria, b) estado no permitido

Donde esto se puede comprobar con la siguiente tabla de verdad

3.- Implementar el latch S-R con compuertas NOR y demostrar su tabla de verdad característica y su diagrama de tiempos.

De acuerdo con la siguiente tabla de verdad se muestra que al mantener todo el switch (J2) en 1 lógico indica que el flip-flop está en estado de memoria por lo que no hay cambio esto se observa en la figura 5. Donde el segundo interruptor se enciende y se apaga y se tiene el mismo resultado en la salida.

Figura 4. Estado de memoria

Pero si todo el switch se apaga se tendrá un estado no permitido en el flip-flop, esto se debe a que en las dos salidas como Q y Q’ tienen el mismo valor por lo que no es un estado valido tal y como se ve en la siguiente figura.

Figura 5. Estado no valido

No hay comentarios:

Publicar un comentario